来源:内容来自半导体行业观察(ID:icbank)综合,谢谢。

在昨天开幕的华为分析师大会上,他们谈到了很多有关芯片的问题。

在回答媒体提问时,华为胡厚崑再次强调,目前华为没有自己建设芯片厂,并表示相信产业的分工是有其自身要求的。

华为常务董事、ICT基础设施业务管理委员会主任汪涛也指出,近几年由于疫情和地缘政治的原因,全球统一的产业链条被打破了,芯片出现短缺。虽然大家看到的是芯片,但实际上半导体产业链条非常长,当中包括设计、制造、封装等,在制造方面也有很多环节,包括华为在内的任何一家公司都不可能靠自己解决问题,需要全产业链上下游共同努力。只有依靠全球统一的供应链,才能解决芯片问题,各地区脱钩与分裂会造成成本的增加和产业进步缓慢。

汪涛同时表示,目前全球各地包括中国都在加大对芯片的投资,提升能力,等这些企业成功了,华为的问题也就自然解决了。

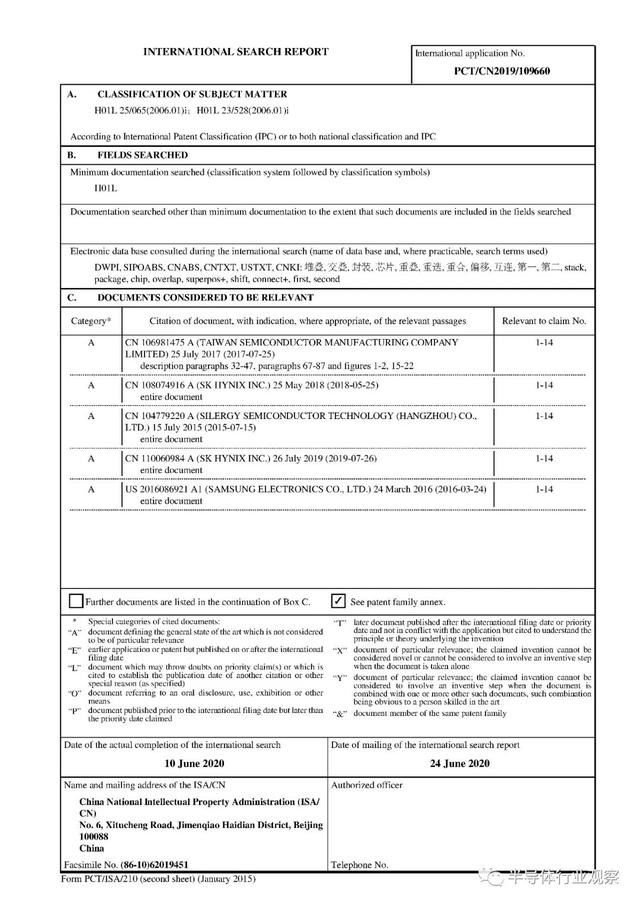

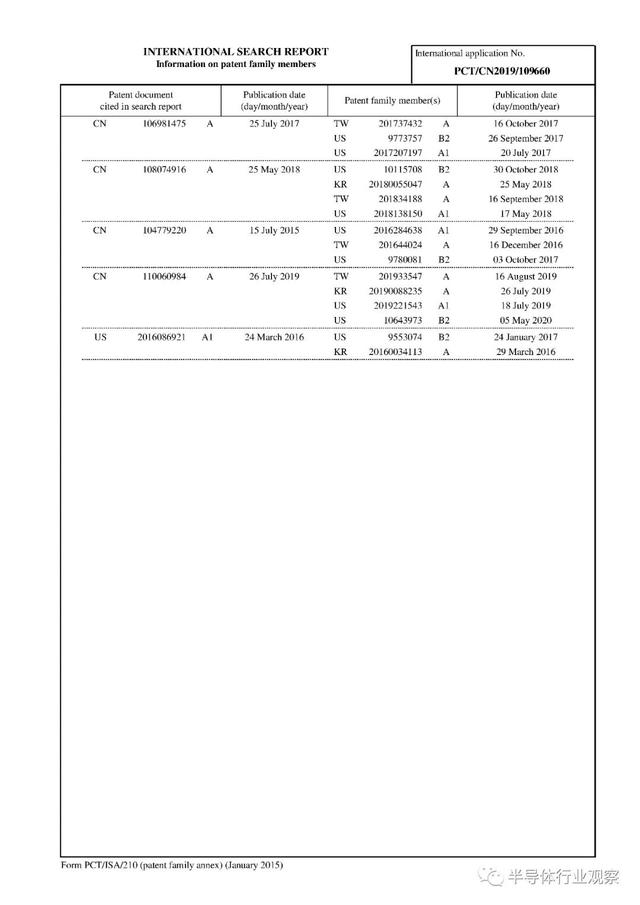

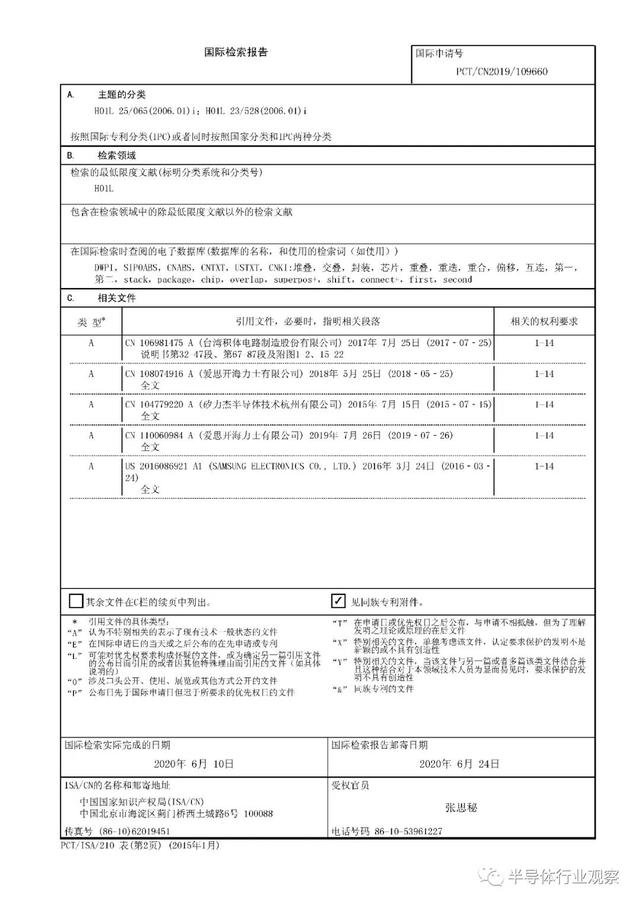

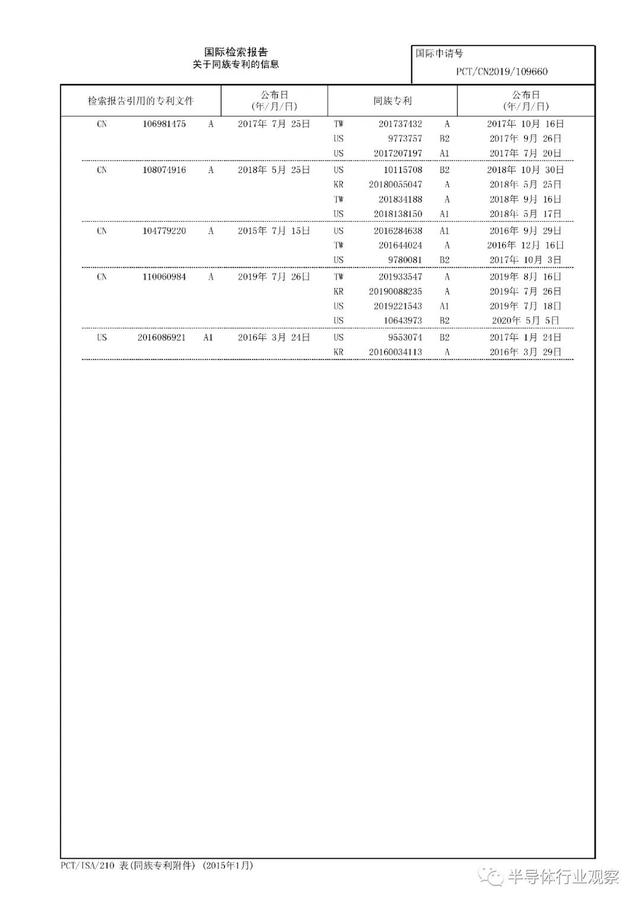

华为方面同时还回应了有关chiplet的问题。他们表示,这个技术是芯片产业发展的必然选择,而最近媒体报道的相关专利则是公司在2019年就申请的。华为方面还指出,公司在chiplet等面向未来芯片的技术方面有很深厚的积累。

华为3D芯片堆叠专利解读

据报道,华为已开发了(并申请了专利)一种芯片堆叠工艺,该工艺有望比现有的芯片堆叠方法便宜得多。该技术将帮助华为继续使用较老的成熟工艺技术开发更快的芯片。

唯一的问题是华为是否真的可以利用其创新,因为没有美国政府的出口许可证,代工厂无法为该公司生产芯片。但至少华为自己当然相信它可以,特别是考虑到这项技术可以为基于不受美国如此严厉限制的旧节点的芯片提供性能提升。

保持竞争力的一种方式我们将在下面详细介绍这项新技术,但重要的是要了解华为为什么要开发这项新技术。

由于美国政府将华为及其芯片设计子公司海思列入黑名单,现在要求所有制造芯片的公司申请出口许可证,因为所有半导体生产都涉及美国开发的技术,华为无法进入任何先进节点(例如台积电的N5),因此必须依赖成熟的工艺技术。

为此,华为前任总裁郭平表示,创新的芯片封装和小芯片互连技术,尤其是 3D 堆叠,是公司在其 SoC 中投入更多晶体管并获得竞争力所需性能的一种方式。因此,该公司投资于专有的封装和互连方法(例如其获得专利的方法)是非常有意义的。

“以 3D 混合键合技术为代表的微纳米技术将成为扩展摩尔定律的主要手段,”郭说。

华为高层表示,由于现代领先的制程技术进展相对缓慢,2.5D或3D封装的多芯片设计是芯片设计人员不断在产品中投入更多晶体管,以满足他们客户在新功能和性能的预期,这也成为了产业界采用的一个普遍方式。因此,华为前董事长强调,华为将继续投资于内部设计的面积增强和堆叠技术。

华为在新闻发布会上公开发表的声明清楚地表明,公司旨在为其即将推出的产品使用其混合无 TSV 3D 堆叠方法(或者可能是类似且更主流的方法)。主要问题是该方法是否需要美国政府可能认为最先进且不授予出口许可证的任何工具或技术(毕竟,大多数晶圆厂工具使用源自美国的技术)。也就是说,我们是否会看到一家代工厂使用华为的专利方法为华为制造 3D 小芯片封装,这还有待观察。但至少华为拥有一项独特的廉价 3D 堆叠技术,即使无法使用最新节点,也可以帮助其保持竞争力。

无过孔堆叠创新的芯片封装和多芯片互连技术将在未来几年成为领先处理器的关键,因此所有主要芯片开发商和制造商现在都拥有自己专有的芯片封装和互连方法。

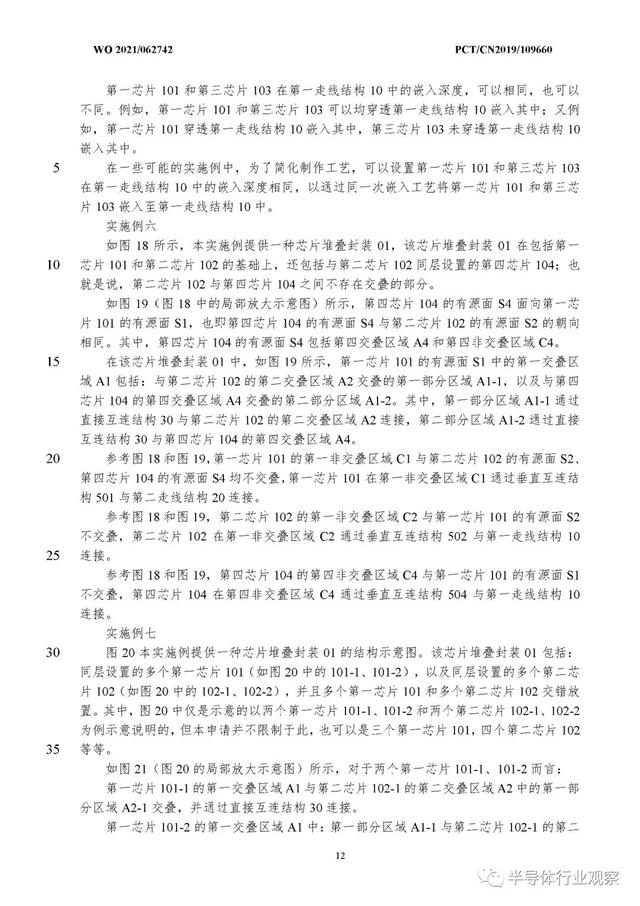

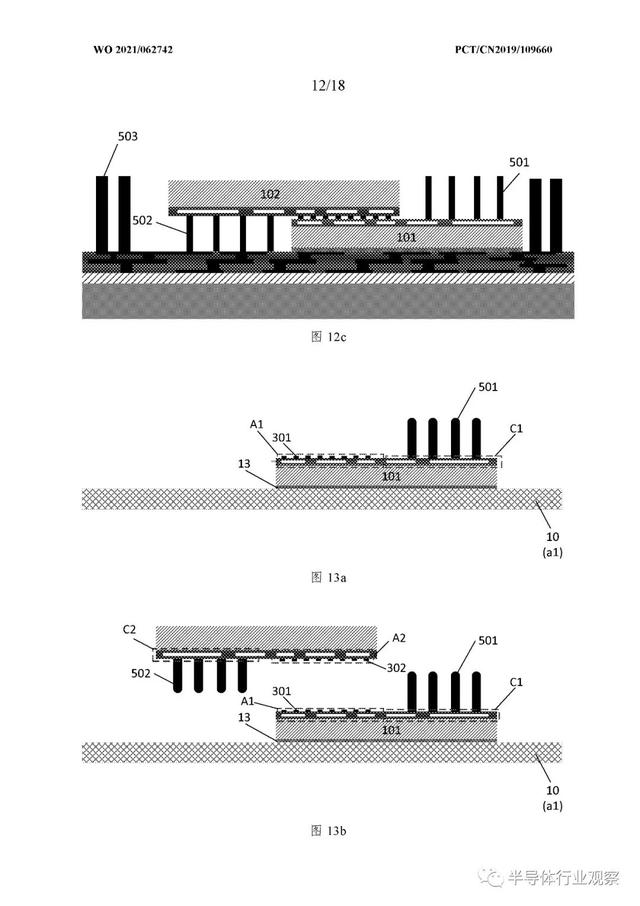

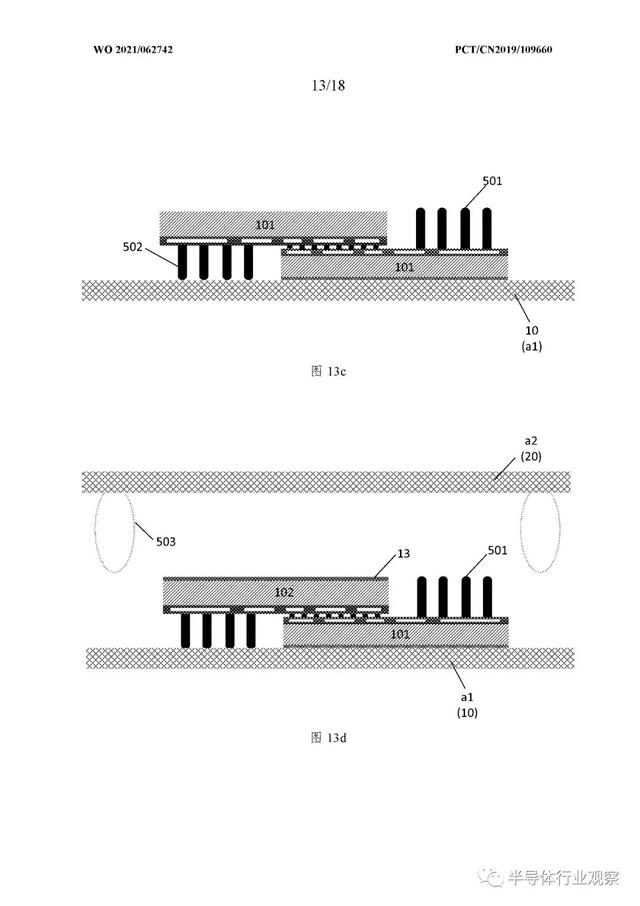

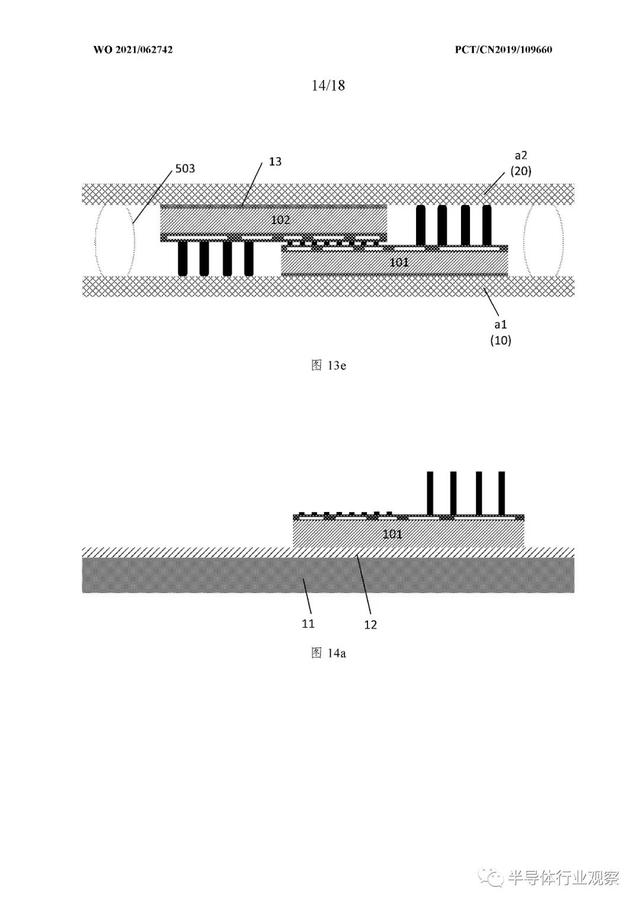

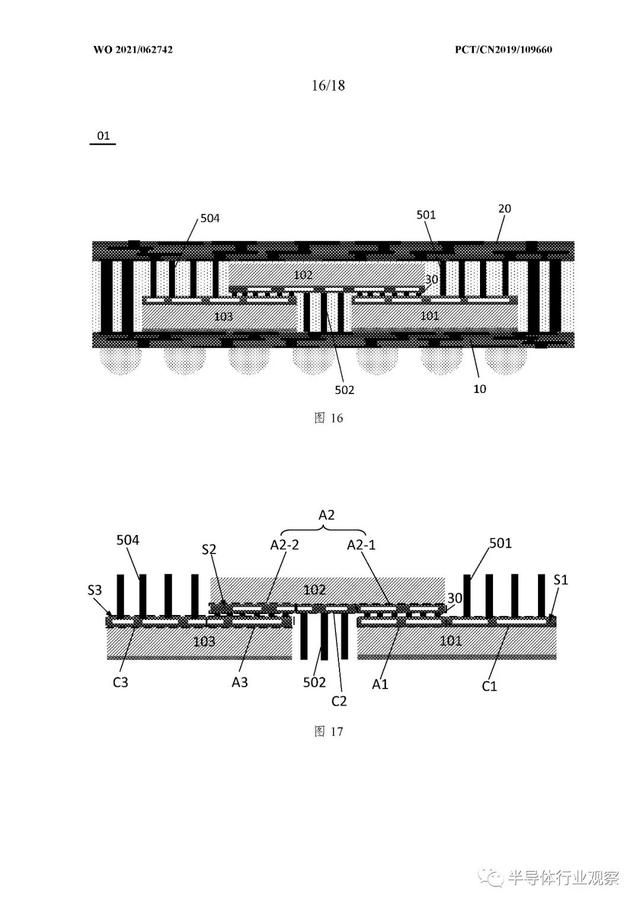

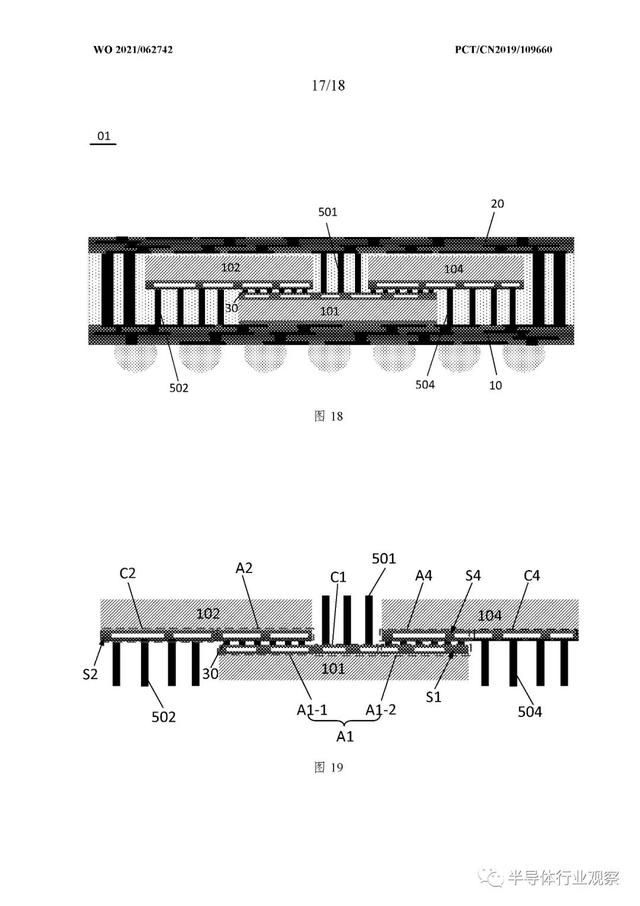

芯片制造商通常使用两种封装和互连方法:2.5D 封装为彼此相邻的小芯片实现高密度/高带宽的封装内互连,3D 封装通过将不同的小芯片堆叠在一起使处理器更小. 然而,3D 封装通常需要相当复杂的布线,因为小芯片需要通信并且必须使用 TSV 提供电力。

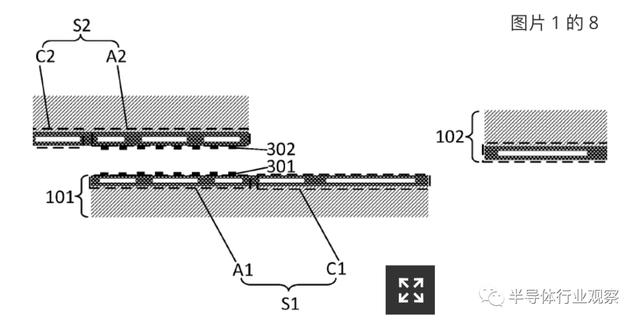

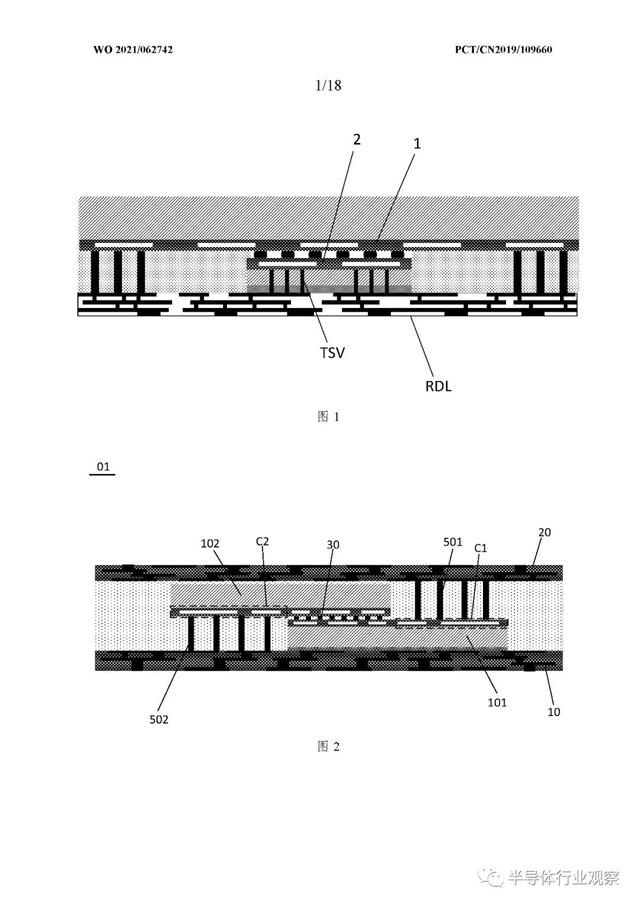

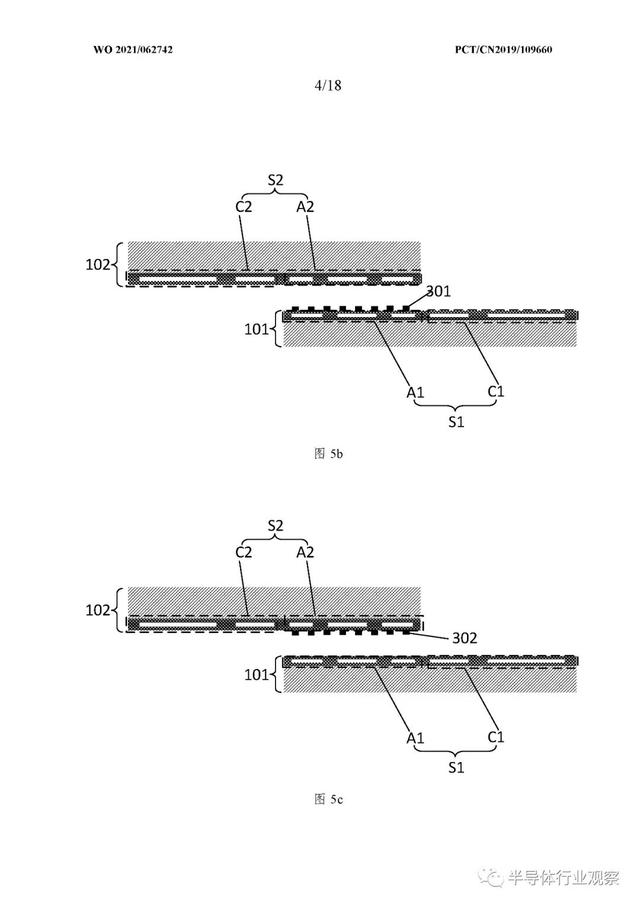

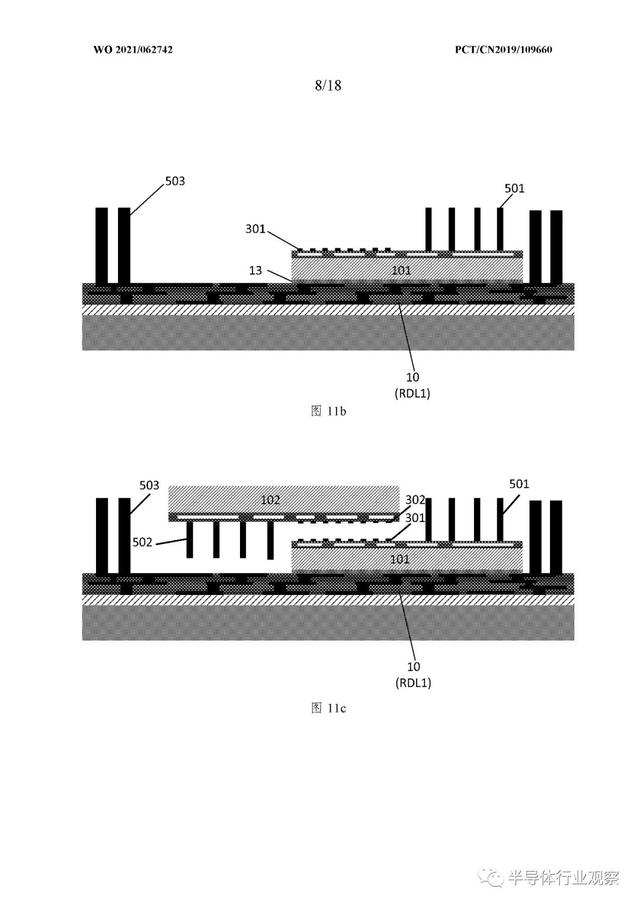

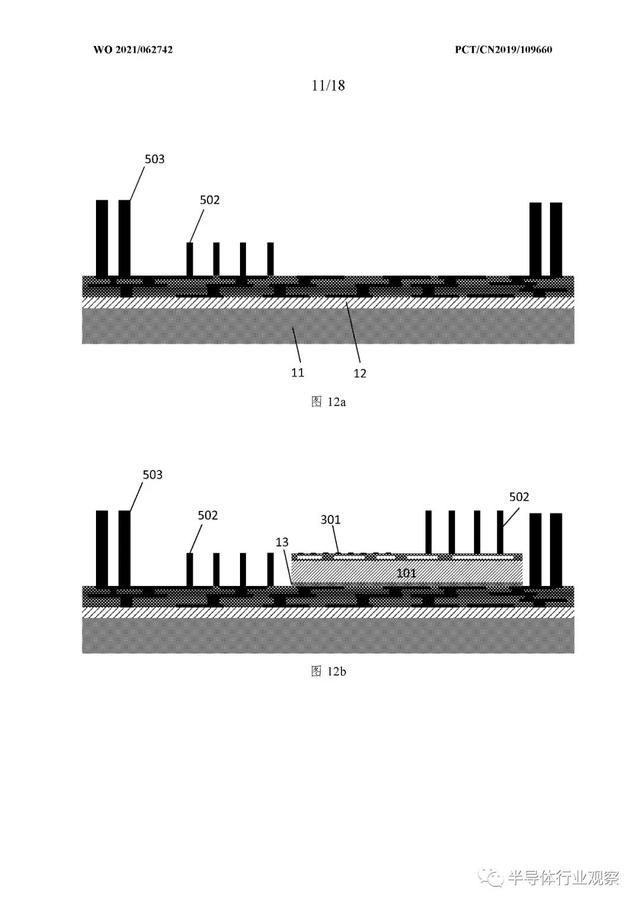

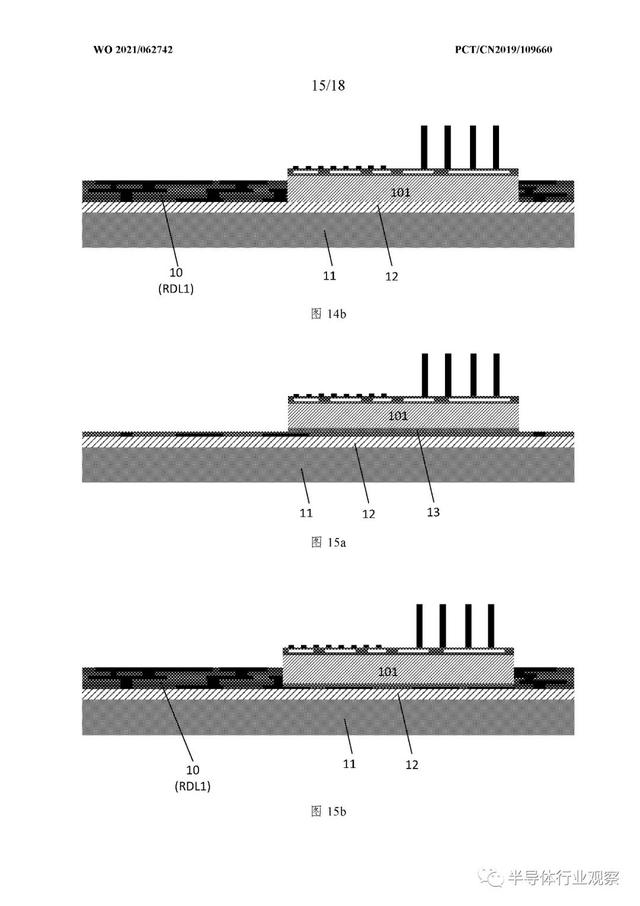

虽然 TSV 已在芯片制造中使用了十多年,但它们增加了封装过程的复杂性和成本,因此华为决定发明一种不使用 TSV 的替代解决方案。华为专家设计的本质上是 2.5D 和 3D 堆叠的混合体,因为两个小芯片在封装内相互重叠,节省空间,但不像经典 3D 封装那样完全叠放。

重叠的 3D 堆叠华为的方法使用小芯片的重叠部分来建立逻辑互连。同时,两个或更多小芯片仍然有自己的电力传输引脚,使用各种方法连接到自己的再分配层 (RDL)。但是,虽然华为的专利技术避免使用 TSV,但实施起来并不容易且便宜。

免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3023内容,欢迎关注。

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装

花粉社群VIP加油站

猜你喜欢